FPGA在信息系統(tǒng)集成中的低延遲優(yōu)勢探析

在當今高速發(fā)展的信息技術(shù)領(lǐng)域,低延遲已成為許多關(guān)鍵應(yīng)用的核心需求,尤其是在金融交易、實時數(shù)據(jù)處理、電信網(wǎng)絡(luò)和邊緣計算等領(lǐng)域。現(xiàn)場可編程門陣列(FPGA)因其獨特的硬件架構(gòu),在實現(xiàn)超低延遲處理方面展現(xiàn)出顯著優(yōu)勢,常常成為信息系統(tǒng)集成服務(wù)中的優(yōu)選方案。相較于圖形處理器(GPU),F(xiàn)PGA在延遲性能上為何能實現(xiàn)數(shù)量級的領(lǐng)先?這需要從其設(shè)計哲學、工作模式及在系統(tǒng)集成中的角色進行深入分析。

從根本架構(gòu)上看,F(xiàn)PGA是一種可編程的半導體器件,其內(nèi)部由大量可配置邏輯塊(CLBs)、可編程互連資源和I/O單元組成。用戶可以通過硬件描述語言(如VHDL或Verilog)直接定義數(shù)字電路的功能,從而實現(xiàn)高度定制化的硬件邏輯。這種“硬件實現(xiàn)”意味著FPGA在執(zhí)行特定任務(wù)時,其操作是直接通過物理電路完成的,無需經(jīng)過指令解碼、調(diào)度等軟件層開銷。相比之下,GPU雖然擁有強大的并行計算能力,但其本質(zhì)仍是一種通用處理器架構(gòu)(盡管針對圖形和并行計算優(yōu)化),執(zhí)行任務(wù)時需要經(jīng)由驅(qū)動程序、操作系統(tǒng)和應(yīng)用程序等多層軟件棧,將計算任務(wù)映射到成千上萬的核心上進行處理。這一過程必然引入額外的延遲,尤其是在處理小批量、高頻率的實時數(shù)據(jù)時,GPU的流水線調(diào)度和上下文切換開銷會變得尤為明顯。

FPGA的并行性是“真正”的硬件并行。在FPGA中,不同的邏輯功能可以同時在不同的硬件資源上執(zhí)行,且互不干擾,數(shù)據(jù)流可以以流水線方式在定制化的數(shù)據(jù)路徑中高速流動。例如,一個網(wǎng)絡(luò)數(shù)據(jù)包處理邏輯可以在接收數(shù)據(jù)的同時進行解析、過濾、修改和轉(zhuǎn)發(fā),所有步驟幾乎同時發(fā)生,延遲僅受限于電路的門延遲和線延遲,通常可達到納秒級。而GPU的并行性更多體現(xiàn)在數(shù)據(jù)級并行上,即對大量數(shù)據(jù)執(zhí)行相同的操作(SIMD),但對于有復雜依賴關(guān)系或需要頻繁決策的任務(wù),其線程調(diào)度和內(nèi)存訪問延遲(尤其是全局內(nèi)存訪問)會成為瓶頸,延遲通常在微秒級甚至更高。

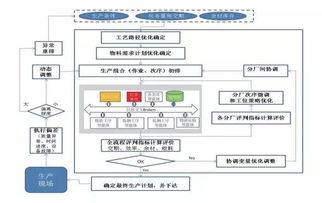

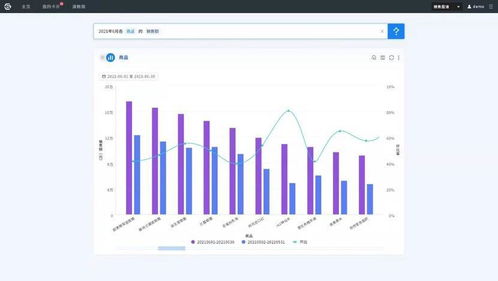

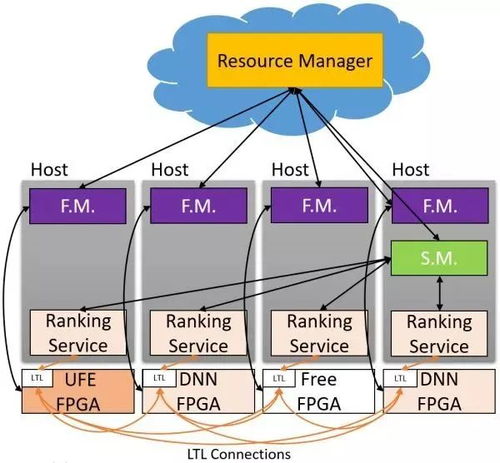

在信息系統(tǒng)集成服務(wù)中,延遲往往受到整個系統(tǒng)鏈路的影響,包括數(shù)據(jù)采集、處理、傳輸和響應(yīng)等多個環(huán)節(jié)。FPGA能夠被集成到數(shù)據(jù)流的關(guān)鍵路徑上,作為專用的硬件加速器或預處理單元。例如,在高速交易系統(tǒng)中,F(xiàn)PGA可以直接與網(wǎng)絡(luò)接口卡(NIC)耦合,實現(xiàn)網(wǎng)絡(luò)協(xié)議棧的硬件卸載,在數(shù)據(jù)包到達的瞬間即進行處理和決策,從而將延遲從軟件實現(xiàn)的幾十微秒降低到亞微秒級別。GPU則通常作為主處理器(CPU)的協(xié)處理器,數(shù)據(jù)需要從網(wǎng)絡(luò)設(shè)備通過總線(如PCIe)傳輸?shù)紾PU內(nèi)存,處理后再傳回,這一過程本身就增加了數(shù)微秒的延遲。

FPGA的可重構(gòu)性為信息系統(tǒng)集成提供了極大的靈活性。在集成了FPGA的系統(tǒng)中,可以根據(jù)不同的應(yīng)用場景快速重新配置硬件邏輯,優(yōu)化數(shù)據(jù)路徑,從而持續(xù)保持最低的延遲。而GPU的架構(gòu)相對固定,優(yōu)化主要依賴于軟件算法和編程模型的調(diào)整,其在延遲上的優(yōu)化空間存在天花板。

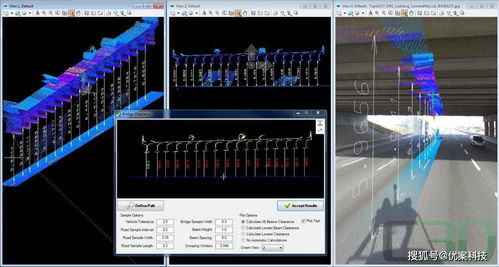

選擇FPGA還是GPU,并不僅僅取決于延遲。GPU在浮點運算吞吐量、編程易用性和生態(tài)系統(tǒng)方面具有巨大優(yōu)勢,適合訓練人工智能模型、大規(guī)模科學計算等對吞吐量要求高于延遲的場景。但在那些對延遲極其敏感、需要確定性和可預測響應(yīng)時間的集成系統(tǒng)中——如自動駕駛的傳感器融合、工業(yè)控制系統(tǒng)的實時反饋、5G基帶的信號處理——FPGA的硬件級低延遲特性使其成為不可替代的選擇。

FPGA之所以能比GPU實現(xiàn)低得多的延遲,根源在于其硬件可編程的本質(zhì)帶來了極致的定制化、真正的硬件并行和精簡的數(shù)據(jù)路徑,使其能夠緊密集成到信息系統(tǒng)的關(guān)鍵鏈路中,消除軟件開銷。在信息系統(tǒng)集成服務(wù)中,深入理解FPGA的這一優(yōu)勢,有助于為高實時性應(yīng)用設(shè)計和部署更高效、更可靠的解決方案。

如若轉(zhuǎn)載,請注明出處:http://m.hngjq.cn/product/44.html

更新時間:2026-04-12 07:05:37